Posted on 2021-03-06 11:34

eryar 阅读(2334)

评论(0) 编辑 收藏 引用 所属分类:

2.OpenCASCADE

OpenCASCADE Connect Edges to Wires

eryar@163.com

1 Introduction

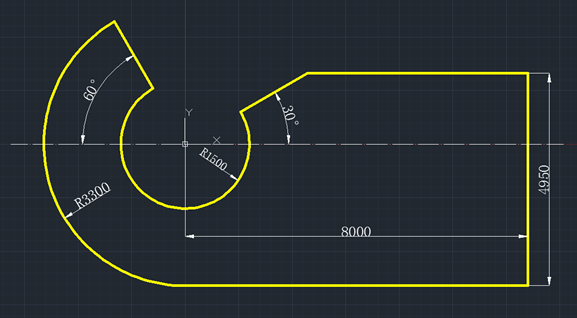

在边界表示法(BREP)中,WIRE是由首尾依次相连的EDGE组成的闭合结构,有的内核也叫做LOOP。BREP结构中,就是通过WIRE来限定FACE的边界范围。FACE中的几何曲面都是用参数曲面形式来表示,简单的通过参数U,V范围来限定,只能得到一些简单规则的曲面片。不规则的任意形状的曲面片,只能通过WIRE来限定。例如,地球这个球面,中国的边境线就相当于WIRE,限定出中国的疆土。

有时在构造WIRE的时候,拿到的是一些无序的EDGE,如何将无序的EDGE生成WIRE,OpenCASCADE中提供了多种方法,下面分别来对这些方法进行介绍。

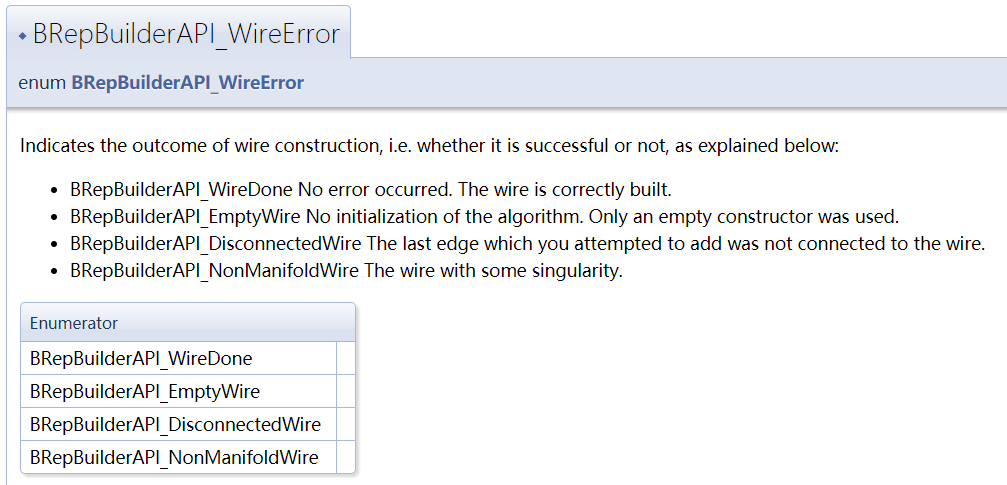

2 BRepBuilderAPI_MakeWire

BRepBuilderAPI_MakeWire是生成WIRE最直接的类,底层使用类BRepLib_MakeWire。生成WIRE的时候有两种方式:一种是依次Add边EDGE;一种是添加一些边,这些边可以是无充的。两种方式的处理逻辑是不同的,对于第一种依次添加EDGE的方式,则要求添加的EDGE是相连的。若不相连或者有其他错误,会直接给出错误信息:

对于添加一些边EDGE的方式,会对添加的EDGE做一个相连检查。

3 ShapeAnalysis_WireOrder

ShapeAnalysis_WireOrder主要用于将无序的EDGE生成WIRE时,EDGE的首尾依次相连的顺序Order。这个类的方式就简单一些,直接根据EDGE的两个端点坐标来检查相连状态。这个功能原来也介绍过:OpenCASCADE中散乱Edge生成Wire

https://www.cnblogs.com/opencascade/p/WireOrder.html

4 ShapeAnalysis_FreeBounds

ShapeAnalysis_FreeBounds这个类中提供static函数ConnectEdgesToWires()用于将无序的EDGES生成一些WIRE。所以这个类可以用于检测一些无序的EDGE中存在几个WIRE。

5 BRepAlgo_Loop

BRepAlgo_Loop用于将一个FACE上的多个EDGE生成多个WIRE。功能与ShapeAnalysis_FreeBounds中的ConnectEdgesToWires类似,但多个要求,这些EDGE都是一个FACE上的EDGE,而且对这些EDGE的Orientation也有要求。若Orientation不是依次相连,则也会生成WIRE失败。

6 Conclusion

综上所述,OpenCASCADE考虑了将无序EDEG生成WIRE的情况。由于是多人协同开发,造成重复的代码实现。建议将重复实现整理归纳,只保留一份稳定性、性能好的实现。

为了方便大家在移动端也能看到我的博文和讨论交流,现已注册微信公众号,欢迎大家扫描下方二维码关注。